CISC stands for Complex Instruction Set Computer. CISC processor is a classification of microprocessor-based of CPU design that operates on large and complex instruction sets so as to execute various tasks using the least possible codes. It is based on more than one instruction per cycle execution approach.

More simply, we can say, the design of the CISC processor is based on the approach to complete the whole operation in few lines of the assembly language code.

Content: CISC Processor

Introduction to CISC

Previously we have discussed the RISC processor i.e., Reduced Instruction Set Computer processor that uses quite a different approach of operation than CISC processor. The RISC processor is the one that uses the approach of increasing internal parallelism by executing a simple set of instructions in a single clock cycle. However, CISC processors, rather than using various simple instructions, utilize complex instruction sets in order to complete any given task.

CISC was introduced in 1970 and it handles instruction execution without making use of multiple codes. It is based on the complex nature of instruction set architecture.

The major goal behind the design of CISC is to have such an instruction set that works well with the tasks and data structures of Higher-Level Languages. This architecture supports a variety of addressing modes and therefore, the instruction length is of variable nature. This signifies that in this case, the whole emphasis is given to the hardware of the system. CISC processors are maturely designed to provide direct hardware support to the developer.

It is known to us that microprocessors are data processors that collect the information, perform the necessary modifications according to the predefined instruction sets, and the results are stored and used in case of further operations within the systems. We know that any operation takes place in a set of paths that includes fetching, decoding, and executing.

In CISC, the compiler’s work is somewhat reduced as the maximum emphasis is given to generate machine instructions to the processor where a single instruction can perform tasks like loading, evaluating, storing, etc. thus, is considered to be complex in nature. However, this reduces the work of the compiler to write long machine instructions for any sort of operation. It incorporates a microprogrammed control unit.

Features of CISC Processor

The CISC processor exhibit the following features:

- Decoding: The instructions are of complex nature, thus offers complex instruction decoding.

- Instruction size: The instructions within this processor are large in size and are of variable nature.

- Data Types and Addressing Modes: It involves more data types and complex addressing modes.

- General Purpose Registers: The operations are performed in the memory itself and the results of operations are also stored within the memory so due to this reason less general-purpose registers are needed in the case of CISC processors.

- Clock Cycle: As the size of instructions here is variable thus more than one clock cycle may be used for instruction execution.

Architecture of CISC Processor

From the above discussion, one must have got the idea that CISC processors are designed in such a way that it needs fewer instructions in comparison to RISC processors to do to the same operation.

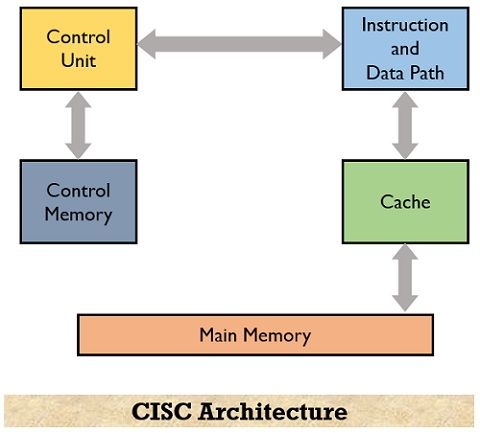

The figure below represents the architectural representation of CISC Processor:

In general, any processor operates in a way that the PC holds the 16-bit address of the instruction which is to be fetched. In the next step, the instruction from the respective address is fetched from the memory and is loaded into the data bus, and further routed towards the decoding unit. Once the instruction decoder gets the instruction, it checks for the opcode that is to be performed and the operand over which the operation is to be executed. However, in the meanwhile, the next data is to be fetched which the opcode requires and so for the same, the control unit generates the necessary control signal.

Along with the ongoing operation, the PC gets incremented by 1 in order to represent the memory address of the next location from where fetching is required. And once the PC holds a new value then that value is loaded into the address latch so as to fresh start the new memory cycle. Furthermore, similar to the previous scenario, the 16-bit address is placed on the address bus which is handed over to the instruction decoder that helps in loading it into the memory. The necessary operation will take place and the result of the operation is stored in the memory.

In this way, the processor operational flow is maintained by successive repetitive cycles.

This CISC architecture offers complex instruction decoding, as multiple addressing modes are required for a single instruction. However, as the operations take place within the memory itself thus, not so many general-purpose registers are required.

CISC Approach

Previously, we have discussed the RISC approach where the compiler’s work is more in simplifying a complex instruction into multiple simple instructions that can be executed in a pipelined manner so as to perform the desired operation at a faster rate. However, in this case, the compiler’s work for instruction simplifying is reduced to a great extent as the hardware is designed to even execute complex instructions.

CISC architecture allows the processor to complete the task in the least possible codes of the assembly language.

In the RISC approach, we have discussed that in order to perform complex instructions, the processor performs various commands that resultantly perform the desired operation.

Suppose MUL is a complex instruction the result of which gives rise to the product of two values. In the case of RISC, the data over which operation is to be performed, present in the memory is first loaded into the register by using separate instructions. Then the adequate command is used to perform the desired operation over the data in the registers. Lastly, the result of the operation is loaded back into the memory.

The CISC approach is quite different from RISC. Unlike RISC, in the case of CISC, there exists no need for loading the data from memory to the register for the operation to take place. Here simply, the data within the memory is directly used for the desired operation to take place. Suppose if we consider the storage scheme of a computer system that represents that the data over which operation is to be performed resides within the memory locations 2:1 and 3:5.

Here in this instruction, no separate load or store commands are needed as just by one instruction:

MUL 2:1, 3:5

The result of the operation is stored in one of the memory locations.

Suppose, x = 2:1 and y = 3:5, then MUL 2:1, 3:5 command is equivalent to

x = x . y

Advantages

- The code sizes are small in the case of the CISC processors.

- Compiler’s work is reduced to a large extent high-level language statement is not required to be converted into assembly language.

- The shortcode length supports less RAM requirement.

Disadvantages

- The high complexity makes the system somewhat inefficient.

- The instruction is executed in more than one clock cycle.

- It does not support instruction pipelining.

Applications

CISC processors are mainly associated with real-time applications such as security systems, home automation, etc.