RISC is an acronym for Reduced Instruction Set Computer. The RISC processor is a type of microprocessor that operates on small but very optimized instruction sets in order to perform various tasks. It is based on one instruction per cycle approach.

RISC is considered to be an alternative to CISC (Complex Instruction Set Computer) which is quite an efficient but somewhat difficult way to perform operations.

Content: RISC Processor

Introduction to RISC

Computer Architecture is a field that deals with the interconnection and controlling of various hardware components to form such a unit (Computer) that can perform the desired operations. Basically, the stored program came into existence around 1950 but that was not the end as major innovations have also taken place after that.

In the year 1970, CISC came into existence which possesses complexity in terms of the instruction set. It was built with the aim to perform instruction decoding in a complex manner. In simplest possible terms, CISC architecture can be understood as a mechanism through which any operation can be executed by using as much as a smaller number of assembly codes as possible. And this is achieved at the cost of making a complex system.

John Cocke, an IBM researcher, who was having excellent knowledge of hardware and software came up with RISC in the year 1974. Mainly, the idea behind the introduction of RISC was to deal with the complexity of CISC. RISC allows an increase in internal parallelism during operation along with a greater number of register sets that facilitate enhanced speed with respect to operation execution by the CPU.

Cocke proved that there are the same instructions that perform 80% of computers work. So, in his approach, he tried to present a simple architecture with a simple set of instructions that can be executed in a single machine cycle. Basically, in this case, the CPU can easily perform a limited set of simple instructions at a faster rate. This means fetching, decoding, and execution all can take place in a single clock cycle and this has made room for faster computation.

Design Rules of RISC Processor

The four major design rules that a RISC processor includes are as follows:

- Instructions: RISC exhibit reduced instruction sets approach. In this case, there are various simple instructions each having a fixed length so one instruction will get executed in a single cycle. This supports the parallel operation. In CISC, the instructions are of multiple sizes and this makes the parallelism in operation quite difficult.

- Pipelining: RISC facilitates instruction pipelining. Basically, here the various subdivided instructions into simple ones are executed parallelly in pipelined format. Through pipelining, during decoding of previous instruction, the next one can be fetched and this provides advancement in operation in each cycle thereby offering maximal throughput.

- Registers: The way the RISC processor operates there exists a requirement of large memory space and thus, it includes a large general-purpose register set. There is no specified register for data or address as here the registers act as a local storage destination for all operations.

- Load-store technique: The whole operation takes place through the data existing in the register. In this case, using individual load and store instructions data is moved between register and memory. This provides an advantage in terms that unnecessarily, multiple memory accesses will not be required.

Architecture of RISC Processor

In RISC architecture, the performance is based on the design principle of simplified instructions that can do less but fast operations in each cycle thereby improving the performance. In Reduced Instruction Set Computer, the word reduced is sometimes misunderstood as eliminating some instructions in order to get smaller instruction sets.

However, in reality, ‘reduced’ here corresponds to the reduction in the amount of work a single instruction performs per data memory cycle. This approach has shown significant improvement in the operating speed of frequently used functions.

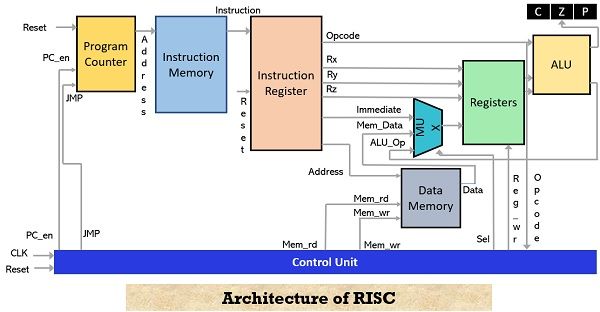

The figure below represents RISC architecture:

In the above given 16-bit processor based on Harvard architecture, we are having 16-bit ALU, 16-bit program counter, 16 general-purpose registers each of 16-bit, 24-bit instruction register, 3-bit flag register for carry, zero, and parity.

The whole processor operation is divided into four states namely, idle, fetch, decode, execute. For any of the operations to take place, the control unit sends the desired control signal while the address of the instruction which is to be fetched is held by the program counter. As it is based on the superscalar approach, thus, by the time decoding of instruction is taking place the next instruction can be fetched from the memory as each instruction is having a fixed size thereby offering parallelism in operation.

It is to be noted here that once a current instruction gets executed, PC gets incremented by 1 in order to represent the address of the next instruction. This is done in a continuous manner until and unless JUMP instruction is encountered, as once JUMP is encountered then the PC is incremented or decremented according to the offset.

The instruction memory stores the instructions and each time after instruction execution, the content of PC is given to instruction memory as input to fetch the next instruction. The IR is responsible for storing and decoding, while the ALU uses the opcode to execute the desired operation for which the control signal is provided by the control unit.

As we have already discussed that here we are having 16 general-purpose registers and the register array has two ports for read and a port for write. When the control unit sends the signal reg_wr then data is written into the register while if the signal is reg_rd then the data of the specified address is read. For any operation to take place, registers provide the desired operands and the result of the execution is stored in the destination register through the MUX.

Examples of RISC processors: ARM processor, MIPS, RISC-V, Atmel’s AVR, PA-RISC, Power-PC, SuperH, SPARC, etc.

RISC Approach

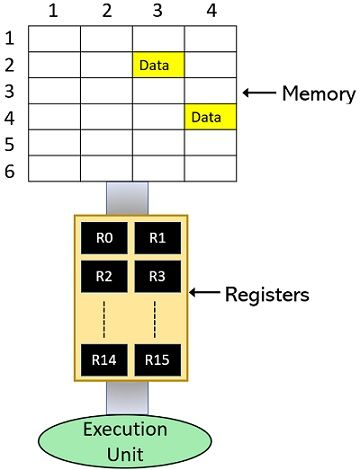

Before understanding the RISC approach, one must be familiar with the CISC approach. So, first, consider the figure below that represents the storage scheme of a computer system:

As CISC architecture tends to perform the required task in few steps of assembly language code thus it uses specific complex instructions to do the same. Suppose SUB is complex instruction used to find the difference of two values.

So, in CISC, just by the instruction:

SUB 3:2, 4:4

The operation will get directly performed within the computer’s memory and stored in one of the memory locations. In this case, the compiler does not have much work to do, and as the code is not lengthy so less RAM will be needed to store the instruction.

Now, this same instruction will have a different format under the RISC approach. The above given ‘SUB’ command can be subdivided as:

LOAD R3, 3:2

LOAD R4, 4:4

By the above commands, the data within the memory bank (3:2 and 4:4) are moved to the registers (R3 and R4) respectively.

SUB R3, R4

By this command, the data existing in these two registers will get subtracted and the result will be in R3.

STORE 3:2, R3

By this, the data is moved from register R3 back to the memory bank.

Here each individual instruction will get executed in one clock cycle thus the operation will be faster but with more RAM utilization. As LOAD and STORE instructions are separated thus, the overall work that the computer performs gets reduced.

Advantages

- It offers maximization in operating speed; this resultantly reduces execution time.

- It is quite a simple approach as a small set of instructions is used.

- The instruction length is fixed thus supports pipelining.

- The addressing modes and instruction formats involved in RISC are simple.

- Each instruction is executed in a single cycle thereby making efficient CPU utilization.

Disadvantages

- The compiler plays a crucial role over here to convert a complex instruction into a simple one. Thus, performance depends on the compiler or programmer.

- It does not allow memory to memory transfer directly, as separate LOAD and STORE instructions are used for moving data from memory to register and vice-versa.

- RISC uses a hardwired control unit hence; instruction modification is not an easy task.

- The instruction size shows a subsequent decrease but the number of instructions in total gets increased. Thus, the overall code length is enhanced.

Applications of RISC

RISC is known to be highly energy-efficient and is used mainly in portable devices. Thus, suitable to integrate within PCs, smartphones, and tablets, their major uses include image and video processing along with telecommunications.